## **Training Schedule**

Lecture 1: VHDL Introduction

Lecture 2: Concurrent" and Sequential VHDL

Lecture 3: RTL Definition

Lecture 4: Signals and Types

Lecture 5: VHDL Operators

Lecture 6: Synthesis VHDL Coding Styles

Lecture 7: Testbench Coding in VHDL

Lecture 8: Advanced VHDL

# VHDL Language

Full VHDL Language

Synthesizable Code

**RTL Code Style**

Corporate Code Style

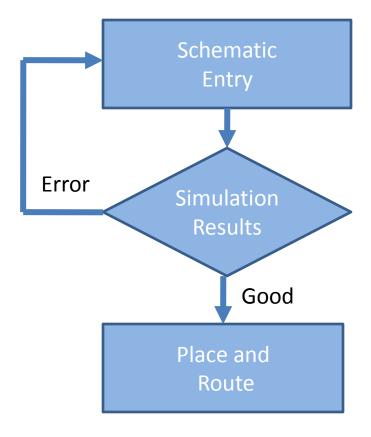

# **Schematic Design Flow**

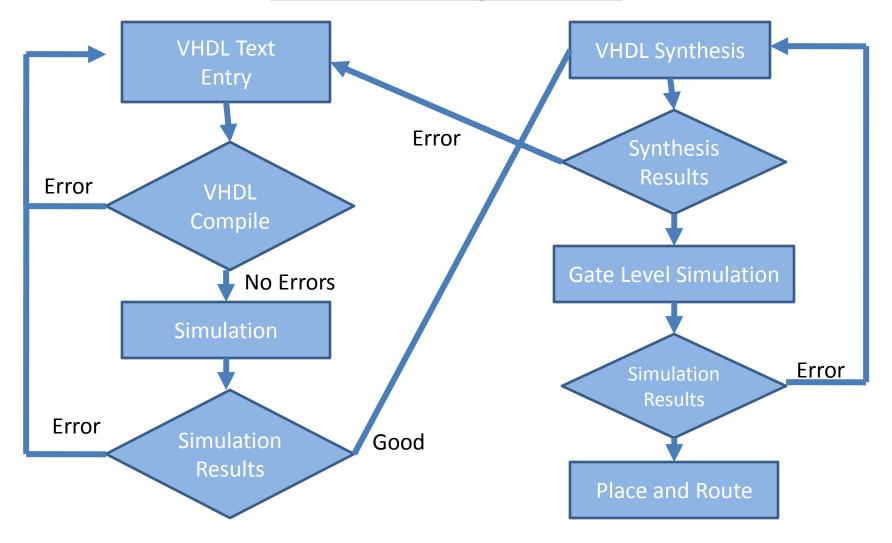

# **VHDL Design Flow**

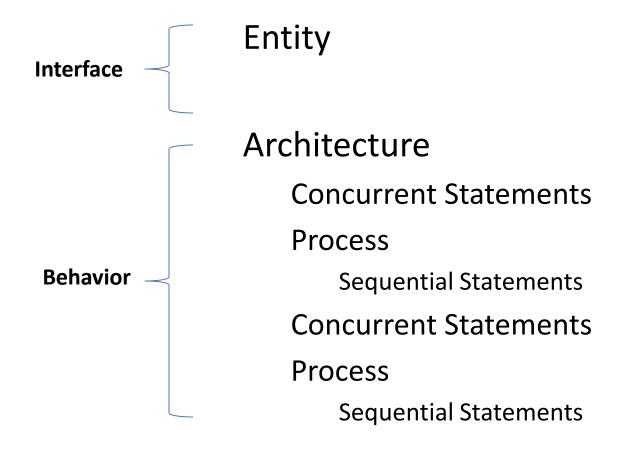

# **VHDL Structure**

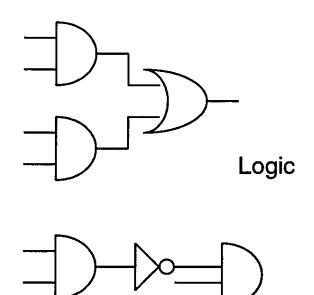

| VHDL          | Schematic           |

|---------------|---------------------|

| Interface     | Symbol              |

| Behavior      | Logic               |

| Configuration | Schematic Hierarchy |

# VHDL Structure (Typical)

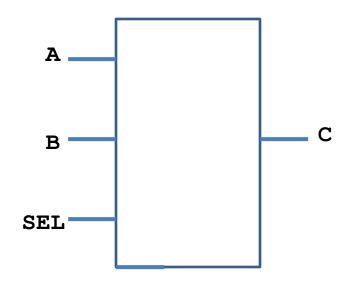

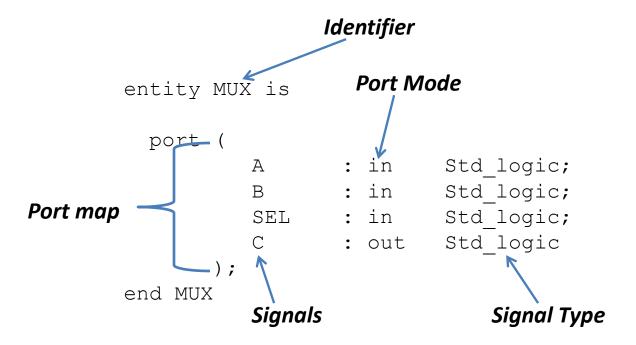

# **Entity**

## **Entity Syntax**

```

entity identifier is

[port (port interface list);

end [entity] [identifier];

```

- Defines the Interface

- Is Associated with one or more Architectures

9/9/2020 Paul Lowson 8

#### **Entity Structure**

## **Architecture Syntax**

```

architecture identifier of entity-name is

begin

{architecture body}

end [architecture] [identifier];

```

- Behavior is defined

- Is Associated with a single Entity

#### **Architecture Structure**

#### **Architecture Name**

#### **Entity Name**

**Architecture**

**Declarations**

```

architecture BEHAV of SEQCON is

signal C : Std logic;

Begin

D \le not C;

process (A, B)

Begin

if A = '1' or B = '1' then

C <= '1';

else

C <= '0';

end if;

end process;

end BEHAV;

```

**Architecture**

Body

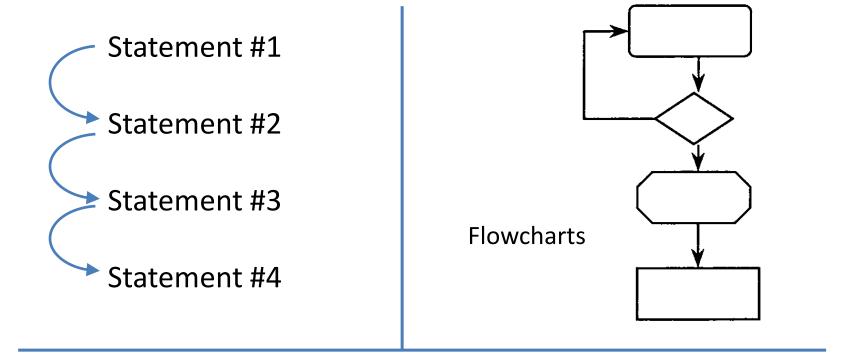

# Sequential Definition

- Statements executed sequentially

- "Software Model"

#### **Concurrent Definition**

Statement #1

Statement #2

Statement #3

Statement #4

- Statements executed simultaneously

- "Hardware Model"

#### **Process Syntax**

```

process_label: process (signal list)

begin

end process [process_label];

```

- Contains Only Sequential Statements

- Executes Concurrently with other Processes

#### Sequential vs. Concurrent

Sequential

```

C \ll (A \text{ and } B);

```

#### **Process Structure**

```

Process Label

MUX_Proc: process (A,B,SEL)

Begin

if SEL = '1' then

C <= A;

else

C <= B;

end if;

end process;

```

#### **Process Characteristics**

What happens when the sensitivity list is incomplete?

#### **Process Rules**

- Process executes when signal in sensitivity list changes

- Process contains only sequential statements

- •Signal assignments occur at the "end process" statement

- •Signals get the last executed assignment

# Concurrent Example

What behavior does this code represent?

# Sequential Example

```

entity SEQEX is

port ( A : in Std logic;

B : in Std logic;

C : out Std logic);

end SEQEX ;

architecture BEHAV of SEQEX is

begin

process (A, B)

begin

if A = '1' or B = '1' then

C <= '1';

else

C <= '0';

end if;

end process;

end behav;

```

What behavior does this code represent?

#### **Concurrent & Sequential Example**

```

entity SEQ2EX is

port ( A : in Std logic;

: in Std logic;

: out Std logic );

end SEQ2EX ;

architecture BEHAV of SEQ2EX is

signal C : Std logic;

begin

D \le not C;

process (A, B)

begin

if A '1' or B = '1' then

C <= '1';

else

C <= '0';

end if;

end process;

end behav;

```

How do Concurrent and sequential statements interact?

## Concurrent vs. Sequential

```

architecture BEHAVl of SEQCONA is -

begin

Concurrent

Z \le X \text{ and } Y;

Z \le X \text{ or } Y;

end BEHAV1;

architecture BEHAV2 of SEQCONA is

Begin

process (X, Y)

Begin

Sequential

Z \leq X \text{ and } Y:

Z \le X \text{ or } Y;

end process;

end BEHAV2;

```

Draw a block diagram for the logic represented by each architecture

# Signal Types and Sizes

Signal Types and Sizes must match

# VHDL Syntax

```

TEST

entity

in

Std logic;

port

: in

Std logic;

В

: out Std logic;

end TEST ;

architecture RTL of ORGATE is

signal C : Std logic

begin

D \le nbt C;

process (A, B)

begin

if A '1' or B = '1' then

C <= '1';

else

C <= '0';

end if;

end process;

end behav;

```

VHDL Language

Syntax is very strict

Find the errors in this code.